UHCI,OHCI,EHCI差異

出處:http://stenlyho.blogspot.tw/2008/08/uhciohciehci.html

USB(Universal Serial Bus)通用串列匯流排:USB1.1規格支援兩種速率:低速(low speed)1.5Mbps和全速(full speed)12Mbps.

新的USB2.0規格除了支援原有的兩種速度外,還而外支援高速(high speed)480Mbps。

USB host controller(USB主控器)必定是下列3種規格:

UHCI : Intel公司提倡,UHCI線路比OHCI線路簡單多了,但是需要比較複雜的驅動程式,對CPU負擔也微重了些,UHCI採用I/O-mapped I/O方式(CPU使用I/O指令來存取USB controller),採用的廠商有Intel,VIA。

在UHCI 中一個SOF 會出現一個Setup Token。

OHCI:Compaq(康柏)公司主導,採用Memory-mapped I/O(CPU使用記憶體指令來存取USB controller),採用的廠商有Compaq,iMace,OPTi,SiS,Ali。

在OHCI 中一個SOF 會可能出現三個Setup token。

EHCI:USB規格,相容於UHCI,OHCI,只有USB2.0(EHCI)才提供高速480Mbps傳輸效率。

A20 Gate v.s A20 Mask

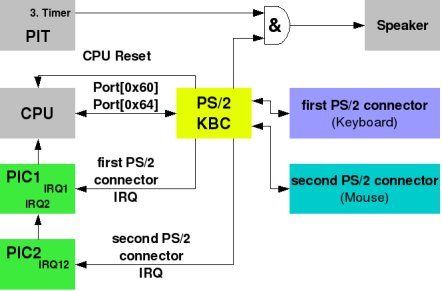

對於圖中我們要區分的是A20 Gate與A20 Mask這兩種不同名詞分別所代表的意義為何。

以下是我自己畫的圖:

這邊描述幾個相關的硬體介面電路所代表的意義: 上圖中可以看到有一個A20 Gate (OR 邏輯匣),他分別有兩支source pin,分別連接到南僑與KBC,且分別由Port 92h與KBC控制狀態,另外還有一支輸出pin連接到CPU的A20 Mask接腳。

這邊描述幾個相關的硬體介面電路所代表的意義: 上圖中可以看到有一個A20 Gate (OR 邏輯匣),他分別有兩支source pin,分別連接到南僑與KBC,且分別由Port 92h與KBC控制狀態,另外還有一支輸出pin連接到CPU的A20 Mask接腳。A20M # 的由來: The Intel 80486 added a special pin named A20M#, which when asserted low forces bit 20 of the physical address to be zero for all on-chip cache or external memory accesses. 看的出來從80486後就改成CPU自己搞….XD

A20 Gate: 一個可以用軟體控制的邏輯匣(AND/OR)…以前A20 gate 輸出腳是接到A20位址線(AND匣,其中一支src pin是接到KBC),後來改接到如上圖的 CPU A20M# 後變成OR匣 (這邊我不確定是否正確,因為我來不及參與過去^^)

A20 Gate 只針對A20有影響,對於其他的A21~A31都沒影響。

這張圖裡面的重點在於EC本身也支援Port 92h功能,也就是說可以設定南橋把Port 92h cycle往EC送(選擇使用EC的Port 92h,此時南橋的Port 92h就失去功效),而EC內有一些組態暫存器,其中有一個是用來控制是否要開啟Port 92h功能,簡單說就是你可以選擇要使用ICH/EC 所提供的Port 92h功能,而使用EC的Port 92h功能時你就必須去設定ICH組態暫存器以及把EC內的Port92_EN_bit 打開。

這張圖裡面的重點在於EC本身也支援Port 92h功能,也就是說可以設定南橋把Port 92h cycle往EC送(選擇使用EC的Port 92h,此時南橋的Port 92h就失去功效),而EC內有一些組態暫存器,其中有一個是用來控制是否要開啟Port 92h功能,簡單說就是你可以選擇要使用ICH/EC 所提供的Port 92h功能,而使用EC的Port 92h功能時你就必須去設定ICH組態暫存器以及把EC內的Port92_EN_bit 打開。

如果你選擇EC內的Port 92h功能時,從圖中可以看見EC內部也有一個A20 Gate,而他的Source pin是跟KBC電路連接在一起,所以控制的方式會如同我前面畫的那張圖ㄧ樣的控制方式。

這部分補充資料是我自己想像所畫出來的圖,實際的電路圖還是要EC Engineer才能夠回答,所以僅供大家參考一下。

Reference

IA32中的5种caching type(也叫memory type)

| Memory Type and Mnemonic | Cacheable | Write Cacheable | Allows Speculative Reads | Memory Ordering Model |

Strong Uncacheable(UC) | No | No | No | Strong Ordering |

Uncacheable (UC-) | No | No | No | Strong Ordering. Can only be selected through the PAT. Can be overridden by WC in MTRRs. |

Write Combining (WC) | No | No | Yes | Weak Ordering. Available by programming MTRRs or by selecting it through the PAT. |

Write-through (WT) | Yes | No | Yes | Speculative Processor Ordering |

| Write Back(WB) | Yes | Yes | Yes | Speculative Processor Ordering |

Write protected(WP) | Yes for reads, no for writes | No | Yes | Speculative Processor Ordering. Available by programming MTRRs. |

- Strong Uncacheable(UC) : 对于UC的内存读写操作都不会写到cache里,不会被reordering.这种类型的内存适用于memory-mapped I/O device,比如说集成显卡。对于被memory-mapped I/O device使用的内存,由于会被CPU和I/O device同时访问,那么CPU的cache就会导致一致性的问题(Note1)。reordering也会导致I/O device读到dirty data,比如说I/O device把这些内存作为一些控制用的寄存器使用.

对于普通用途的内存,UC会导致性能的急剧下降。Note: 一种例外是,有些I/O device支持bus coherency protocol,可以和CPU保持cache一致性,这样的话是可以使用cacheable的内存的,但是这种总线协议也是有代价的。 - Uncacheable (UC-): 和UC类型一样,除了UC- memory type可以通过设置MTRRs被改写为WC memory type.

- Write Combining (WC): WC内存不会被cache, bus coherency protcoal不会保证WC内存的读写。对于WC类型的写操作,可能会被延迟,数据被combined in write combining buffer, 这样可以减少总线上的访存操作。Speculative reads are allowed(Note)。

对于video frame buffer, 适合使用WC类型的内存。因为CPU对于frame buffer一般只有写操作,没有读,并不需要cache。对frame buffer而言,的写操作是否按顺序没有关系。

(Note: Speculative read是指读之前并不验证内存的有效性,先冒险的读进来,如果发现不是有效数据再取消读取操作,并更新内存后再读取. 比如说数据还是被buffer在WC buffer中) - Write-through (WT) and Write-back(WB)

WT Writes and reads to and from system memory are cached.

Reads come from cache lines on cache hits

read misses cause cache fills

Speculative reads are allowedWrite combining is allowed.All writes are written to a cache line (when possible) and through to system memory.When writing through to memory, invalid cache lines are never filledand valid cache lines are either filled or invalidated. Write combining is allowed.(Write misses doesn’t cause cache line fills)适用于bus上的设备只读取内存而不需要写

(Note: Windows上似乎没有使用这种类型的内存)WB Same as WT Write combining is allowed.Write misses cause cache line fillsand writes are performed entirely in the cache, when possible最普通的只会被CPU使用的内存,由于write操作是在cache中进行的,只有必要的时候才会被写会memory,可减少了bus的上的压力 - Write protected(WP): 读操作和WT/WB没有什么区别,读会被cache. 写不一样,写的时候会在bus上传播这个操作,并且导致其他处理器上的cache lines被更新。

主要用于多处理器的情况。WP的内存,在写的时候就会更新其他处理器上的cache,而WB/WT类型的内存需要等到其他处理读的时候才会去更形无效的cache

GoMCU

GoMCU